目前運用在實際產品製造的製程流程,已經與一開始所建議用在通用3D IC的流程有很大的不同。目前已經有許多成功的 3D-IC 原型被運用在很多不同的元件上。然而,在某些應用上,3D-IC 架構儘管仍具有技術複雜性和無所不在的成本壓力,但也已順利整合進產品當中,而對於其他產品則似乎還有著一張很長的問題清單(成本、良率、散熱問題、缺乏標準、缺乏設計工具等等),而這也阻礙了 3D-IC 未來的整合。 |

|

在一般的看法中,一種技術的創新會首先導入到高效能、高利潤的應用上,因為其效能的增加能夠承擔額外的成本。隨著技術的日趨成熟,成本會降低,而且越來越多的應用會採用新技術。在半導體業中的一個很好的例子是覆晶凸塊(flip chip bumping)。然而,如果我們以 3D IC 來看,其情況並不是那麼清楚。雖然在科學、軍事或醫學領域上有一些「不計成本」的 3D 堆疊(stacking)應用,然而許多高級元件(尤其是 CPU)仍尚未使用 3D 堆疊。但另一方面,一些在我們業界中最低成本的元件,如發光二極體(LED)、微機電系統(MEMS)和影像感測器均已成功地運用了 3D-IC 技術。

在大量生產的低成本元件上採用 3D-IC 技術,具有技術成熟度的證據了嗎?哈佛教授 Clayton Christensen 在他著名的《創新者的困境》一書中導入了任何創新與其在工業運用上的潛在可能性,應該在各自的價值網路背景上加以評估的概念 [1]。一個產品的價值網路(例如 CPU),是由銷售的關鍵參數(例如運算能力、時脈速度、晶片上的快取記憶體和價格),以及目前用戶對未來需求的期望所定義。任何能夠改善目前價值網路中的銷售關鍵參數的創新,就被定義為「持續性創新」。而無法改善當前價值網路內的銷售關鍵參數的創新則被定義為「破壞性創新」。

Christensen 教授在他的研究中所得出的結論是,當創新被認為是「破壞性」時,則將無法導入到價值網路中,不管其技術如何成熟、便宜,或者它們已有完整架構可運用在其他應用上。然而,當創新在不同的價值網路上是持續性時,則用戶將能磨練自己的技能,並建立專業知識。如果在某一價值網路中的期望發生變化時,則創新將能夠被非常快速地導入。

例如,對於 FPGA 來說,2.5D 的中介層(interposer)能夠具有更小的晶粒尺寸,而其能夠讓 28nm 技術在較早期的時間點上,以合理的晶圓良率加以導入。FPGA 導入中介層的結果是,具有更多且更快電晶體的 FPGA 可以更早被製造出來。因此,具有 2.5D 中介層的 FPGA 是一種持續性創新。對於如記憶體的主流半導體元件來說,摩爾定律是一個很好的代理價值網路(或至少目前為止)。假如你在晶片上加上一個矽晶穿孔(TSV)後,則你將不能把電晶體放到同一區域上。TSV 會降低晶片上的電晶體數目,因而增加每個電晶體的價格。

3D整合已經能夠量產了嗎?

乍看之下,TSV 和 3D IC 是破壞性創新。TSV 與晶粒堆疊已經成功地運用在大量製造的 CMOS 影像感測器上,儘管結合了高技術複雜性、未成熟技術,以及低成本/低利潤元件的事實,似乎是一個非常不利的局面。若從純技術的角度來看,3D-IC 影像感測器似乎比其他元件,如堆疊式記憶體還要更具挑戰性。當 TSV 的密度愈高時,則 TSV 的直徑會更小、間距更小、晶圓更薄,因此晶圓間的堆疊就成為必要的。然而,從前端照射式影像感測器到背照式影像感測器的轉變,以及目前轉換到 3D 堆疊式影像感測器(其光電二極體和訊號處理是在個別的晶圓上製造),已經在現存的價值網路中產生了技術性改進,包括更好的解析度、更小的像素、更好的訊雜比、更快的影像處理速度和更高的頻寬。

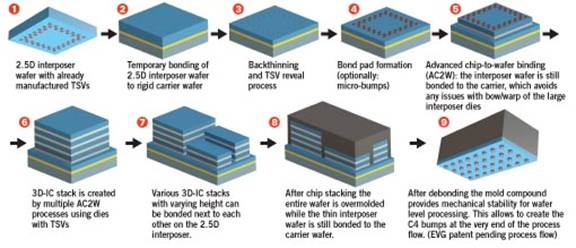

圖1:具有 3D 堆疊晶片的 2.5D 中介層的示範製程流程(澳洲EV Group公司 正在申請專利中)[2]

當工程師首先檢視了 3D IC 技術的開發時,他們並沒有從一開始就設計一個 3D-IC 元件,而是從個別的技術里程碑開始。在大多數情況下,第一個里程碑是製造一個具有10、1000 或 10000 個 TSV 的菊狀鏈。其重點主要是在 TSV 製造的單元製程上。而第二個里程碑是製造一個具有 TSVs 的薄晶粒並在兩端產生凸塊,其最終將可能會被運用於實際的系統上。在早期 3D/TSV 開發時的薄化晶圓處理的典型方式,是利用一種暫時性鍵結的晶圓,以承受任何形式的背面處理製程。因此,彈性和寬廣的製程窗是最重要的。理論上,完整製造個別薄晶片的想法是非常具有吸引力的,因為它能讓良品裸晶(KGD)的製造成為可能,並且能夠適合每一種可能的整合方案和企業情境。然而,實務上這種方法會造成過於複雜的整合方案,從良率和成本的角度來看這並不是最佳化的方案。

當典範在產品組合開始針對特定產品採用薄化晶圓處理時就已經產生了改變。現在的最高目標是要將產品利潤最大化,而且良率和擁有成本也針對晶片與封裝的整個製程流程進行優化─通常會放棄先前認為的通用型放諸四海皆準的解決方案,並且產生全新的整合方案。例如,以前的研發工作著重在很厚的薄膜,以及嵌入 C4(覆晶)凸塊的想法,而目前的 3D-IC 元件主要是應用凸塊後置(bump-last)的製程流程,其使用非常薄的黏著層。此方式具有成本降低、更好的薄膜厚度控制和更高的良率等優點,並且避免了凸塊之後的處理所造成的凸塊損傷。從非常厚到薄的膜層轉換也降低了薄膜固化烘烤步驟的持續時間 ─ 也讓暫時性黏著晶圓的設計成為可能,並提高了超過二倍的產出。圖一展示了具有藉由晶片到晶圓打線的 3D-IC 晶片堆疊之 2.5D 中介層的示範製程流程 [2]。

另一個關鍵的 3D 整合概念是剝離前的包覆成型(overmolding),其允許在超薄晶圓上進行雙面加工,同時避免了薄晶圓一起處理的問題。如同圖二中所示,在晶片堆疊之後,整片晶圓是包覆成型的,而薄的中介層晶圓則仍然是鍵合在載具晶圓上。這種包覆成型的化合物會在薄的中介層晶圓上方產生堅硬的膜層。

圖2:剝離製程前的包覆成型是一個關鍵的整合概念。

全文請參閱《半導體科技雜誌 SST-AP Taiwan》

參考文獻

- C. Christensen, "The Innovator's Dilemma," Harvard Business School Press, 1997

- T. Matthias et al., "From unit processes to smart process flows – new integration schemes for 2.5D interposer," Chip Scale Review, March/April 2013

更多歷期精采文章,請參閱智權報總覽 >>

|