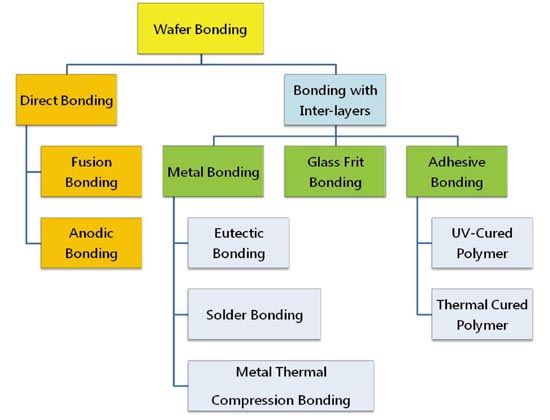

1990年代初期微機電系統(MEMS)接合市場的應用,開啟了工業上最早晶圓接合技術發展之里程碑。當初只局限於直徑100 mm、150 mm和200 mm等晶圓,而且大部份晶圓接合之製程需求是由元件結構特性而定。近年來由於晶圓之光學構裝(例如:CMOS影像感測器)應用與3D IC技術的迅速發展,快速帶動晶圓接合技術的應用領域,朝向300 mm晶圓及各種先進TSV技術整合上發展。從MEMS構裝、晶圓級構裝、以及3D整合構裝,由於應用領域的不同,其個別需求亦不同,所幸目前已發展出多樣化的晶圓接合製程,以提供不同應用需求之最佳解決方案。如圖一所列出各種晶圓接合製 程,這些製程皆有其特定的物理與化學機制,當兩片基板進行接合時,可藉由分子鍵結或原子鍵結接合、合金化接合、氧化物接合、或黏著材料等方式進行接合。

一般晶圓接合製程的使用限制,主要是受到退火溫度所影響。退火溫度 的高低取決於接合原理與材料特性,熱退火對晶圓接合的主要影響是材料的熱膨脹行為。當溫度昇高時,不同熱膨脹係數之兩材料間會產生熱應力,進而影響接合可 靠度。有鑑於此,過去數十年來,有許多的研究都致力於發展低溫接合製程,以擴大晶圓接合的應用領域。傳統低溫接合溫度範圍在RT~400℃,近年來已發展出溫度低於400℃之新晶圓接合製程,以充份符合晶圓級3D整合之新領域需求。

目前能夠應用於3D-IC整合的晶圓接合製程,則包括:(1)熔融接合(Fusion Bonding);(2)金屬熱壓接合(Metal Thermal Compression Bonding);(3)聚合物黏著接合(Polymer Adhesive Bonding);及特殊共晶接合等。本文將參考最新文獻 [1~10],介紹3D IC構裝應用相關之晶圓對位與接合技術,以深入瞭解目前技術的發展趨勢。

圖一:依接合原理分類之名種晶圓接合方法 [1, 2]。

晶圓對位製程(Wafer Alignment Process)

晶圓對位(Wafer Alignment)技術,有機械對位(Mechanical Alignment)及光學對位(Optical Alignment)兩種。

機械對位(Mechanical Alignment): 使用晶圓的凹槽(Notch)或平邊(Flat) 作為對位的基準,採用特殊定位插銷(Special Pins)作晶圓對位。針對12吋晶圓,SEMI規範(SEMI Standard)所要求的對位精準度為±50μm。

光學對位(Optical Alignment):使用光學儀器將兩晶圓進行精確對位,對位精準度範圍為1~10μm。由於光學對位精準度需求較高,所以定位記號都製作於圖案化晶圓上,定位記號的尺寸及位置,則依精準度需求而定。

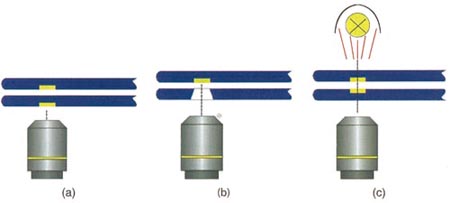

光學對位可分為直接對位(Direct Alignment)及間接對位(Indirect Alignment)兩種。其中,直接對位(Direct Alignment)最少需要有一片晶圓能讓可見光(Visible Light)或紅外線(Infrared Light;IR)通過,兩片晶圓的對位點可以同時觀察到。間接對位(Indirect Alignment)是指兩片晶圓無法讓可見光或紅外線通過,它採用第二片晶圓在參考點的預存數位影像(Digitized Image of the Second Wafer),作為第一片晶圓對準依據,間接方式達到對位目的。常用的光學對位方法有:背面對位(Backside Alignment)(圖二(a))、透明晶圓對位(Alignment with Transparent Wafer)(圖二(b))、紅外線(IR Alignment)對位(圖二(c))、面對面對位(Face to Face Alignment)等(圖三)。其詳細製程分別敘述如下:

(1)背面對位(Backside Alignment):第一片晶圓正面有對位記號,第二片晶圓背面有對位記號,先儲存第一片晶圓之數位影像,然後將第二片晶圓對準第一片晶圓之數位影像,使用高精密度的X-Y機械移動工具,將第二片晶圓的對位記號對準第一片晶圓數位影像中的對位記號,使兩晶圓的對位記號重疊,進而達到晶圓對位目的(如圖二(a))。

(2)透明晶圓對位(Alignment with Transparent Wafer):對位方式與背面對位相似,由於底部第一片晶圓為透明晶圓,所以不需要第一片晶圓之數位影像,第一片透明晶圓可讓可見光通過(例如圖二(b)玻離晶圓),對位方式就是將兩片晶圓的對位記號重疊,使用高精密度的X-Y機械裝置移動晶圓,將底部晶圓的對位記號重疊到上部晶圓,可同時觀察兩片晶圓對位記號的動態影像。

(3)紅外線(IR Alignment)對位:晶圓可讓紅外線通過(例如圖二(c)低雜之矽晶圓)。對位方式就是將兩片晶圓的對位記號重疊,使用高精密度的X-Y機械裝置移動晶圓,將底部晶圓的對位記號重疊到上部晶圓,可同時觀察兩片晶圓對位記號的動態影像。

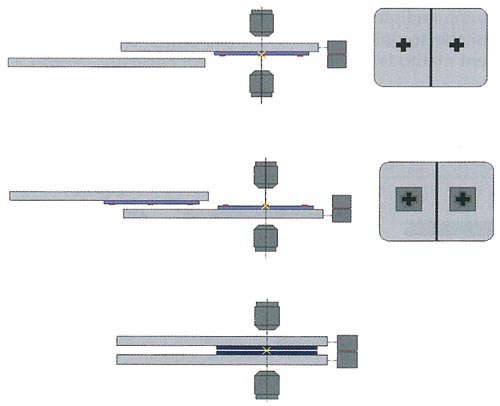

(4)面對面對位(Face to Face Alignment): 採用Smart View晶圓面對面軍(Face to Face) 高精密對位機原理(圖三),使用兩個顯微鏡來觀察兩片對位晶圓之對位點,由於面對面對位的兩片晶圓的對準記號,都在晶圓的正面,當晶圓接合後,兩片晶圓的 對準記號將被接合面覆蓋。首先使用下方顯微鏡對準上部晶圓的對準記號,而上方顯微鏡則對準底部晶圓的對準記號,將兩片晶圓的對準記號與外部參考點的相對位 置儲存起來,接者將兩片晶圓移動來對準參考點所儲存的位置,此種晶圓對位的精度可達到小於1μm。由於Smart View高精密對位機原理是處理晶圓的正面,所以適用於任何種類之基板,一般紅外線IR光遇到金屬會產生光散射,而矽基材如果有掺雜時,則會降低紅外線IR光,所以會影響到對位影像之對比,使用Smart View對位機原理可彌補以上缺點。圖四為Smart View重覆對位400次之記錄,其左側與右側的對位精度(Alignment Accuracy)可以達到小於120 nm [3]。

圖二:常用的光學對位方法:(a)背面對位(Backside Alignment)、

(b)透明晶圓對位(Alignment with Transparent Wafer)、(c)紅外線(IR Alignment)對位等 [2]。

圖三:Smart View晶圓面對面(Face to Face)對位原理 [2]。

圖四:Smart View重覆對位400次之記錄 [2]。

因為晶圓對位(Wafer Alignment)與晶圓接合(Wafer Bonding)之特性不同,所以無法同時進行兩種製程。晶圓接合設備需要有迅速與均勻的加熱系統,能夠提供高而均勻的壓力,以及後續製程氣體導入,與快速抽真空等靈活性需求,所以很難與晶圓對位設備合併於同一設備中使用。一台晶圓對位設備可支援多台晶圓接合設備,晶圓接合座(Bond Chuck)必須要有良好設計,因為它會影響到最終晶圓對位精準度。從晶圓對位設備將晶圓傳送到晶圓接合設備,以及進行晶圓加熱時,必須要有設計可靠的晶圓接合座(Bond Chuck)為基礎,以確保大量生產時晶圓對位精度不致發生偏移。以下將介紹晶圓對位(Wafer Alignment)與晶圓接合(Wafer Bonding)之製程流程(圖五):

(1) 首先將晶圓放入晶圓對位設備中。

(2) 進行晶圓對位(有手動對位及自動對位兩種),將對位好之晶圓使用機械方式固定於晶圓接合座(Bond Chuck)上,如果需要在接合界面(元件內部)進行環境氣氛控制時,可在接合界面區放入間隔物(Spacer),並以機械方式夾緊(Mechanical Clamp)固定。

(3) 將晶圓接合座(Bond Chuck)放入晶圓接合設備之腔體中,接者抽真空到所需要的腔體真空度,取出接合界面區之間隔物,進行加熱及施加壓力於晶圓兩側,以完成晶圓接合製程。

為了確保晶圓對位合乎製程需求,必須考慮一些重要因素。首先在晶圓設計時,必須先定義對位方式(Alignment Method),然後將晶圓接合之對位點設計於晶圓Layout展開圖上。可由基板種類(Substrate Type)、特殊性質(Specific Features)、對位精度(Alignment Accuracy)等重要因素,進而決定所要採用的對位方式及對位點設計。針對某一特定的對位方式,其所能達到的定位精度及可靠度,這主要取決於對位點形狀與尺寸之設計,以及晶圓上對位點的位置。整個晶圓接合製程是否嚴格控制每一個細節,將影響接合後之對位精度(Post Bonding Alignment Accuracy)[2]。

圖五:晶圓對位(Wafer Alignment)與晶圓接合(Wafer Bonding)之製程流程。

晶圓接合製程中的許多因素都會影響最終的對位精度,其中以中間接合層的 壓縮應力最容易導致晶圓對位偏移,而中間接合層是指:共晶接合層、黏著接合層、玻離粉接合層等。此外,兩接合層之熱膨脹係數如果不匹配,亦會影響對位精 度。一般針對接合製程會定義兩項規格:第一為對位後精準度(Post Alignment Accuracy);第二為兩接合晶圓之界面經硬化後,所量測出來的接合後精準度(Post Bonding Accuracy)。

3. 晶圓接合製程(Wafer Bonding Process)

目前能夠應用於3D-IC整合的晶圓接合製程,則包括:(1)熔融接合(Fusion Bonding);(2)金屬熱壓接合(Metal Thermal Compression Bonding);(3)聚合物黏著接合(Polymer Adhesive Bonding);及特殊共晶接合等。以下針對熔融接合、金屬熱壓接合及聚合物黏著接合等製程,進行個別介紹:

3.1. 熔融接合(Fusion Bonding)[2, 3, 4]

熔融接合為工業上最早使用的晶圓接合技術,兩晶圓表面因化學鍵結(Chemical Bond)的建立,進而形成晶圓接合,熔融接合製程包含兩個步驟:

(1) 在常溫下將兩晶圓對準接觸,先形成較弱的接合,此步驟又稱為預接合(Pre-Bonding)。

(2) 在高溫600~1200℃(溫度則與晶圓之表面材料有關)下,進行熱退火(Thermal Annealing)幾個小時,將弱鍵結(Weak Bond)變成共價鍵(Covalent Bond),進而形成強而堅固之接合。熔融接合對於晶圓表面之潔淨度及平坦度的要求較高,必須防止化學污染物,以免影響接合機制。

熔融接合所需的退火溫度非常高,並不適於3D IC整合應用上。近年來為了擴大其應用領域,目前已修改一些製程,來降低退火溫度(Anneal Temperature)到小於400℃。例如在預接合(Pre-Bonding)製程前,先採用電漿活化(Plasma Activation)晶圓表面,即可降低退火溫度。如圖六所示,使用電漿活化改變晶圓表面之化學構造,以形成高能量鍵結,如此便可降低退火溫度及縮短退火時間。

標準的親水性熔融接合堵Hydrophilic Fusion Bonding),必須在溫度大於1,000℃下,進行8~10小時的退火,才能達到最大鍵結強度。然而,如果預先採用電漿活化(Plasma Activation)處理,則在200~400℃溫度下,進行0.5~3小時的退火處理,亦可達到相同的鍵結強度。圖七為不同退火溫度(100、200、300、400℃)下,晶圓接合強度(表面能)與退火時間之變化圖。為了要使此熔融接合製程能應用於3D IC整合上,在晶圓接合前必須先進行晶圓平坦化處理,使晶圓表面粗燥度達到1nm。一般採用CVD沉積氧化物,然後進行CMP平坦化製程,重覆多次氧化物沉積與CMP平坦化製程,使晶圓表面平坦度合乎規格需求。此低溫熔融接合製程使用剛性接合面,可在常溫下進行預接合步驟,所以對位精度高,可以批次方式進行熱退火,產能可高達14~25 Bonds/Hour。

3.2. 金屬熱壓接合(Metal Thermal Compression Bonding)[5]

將兩相同金屬材料施以加熱及加壓,它是一種固態擴散反應(Solid State Reaction),會在接合界面產生原子交互擴散(Inter-Diffusion of Atoms)與晶粒成長(Grain Growth)來進行接合。此接合技術是將堆疊晶圓在高溫下,施以高壓力一段時間,進而形成晶圓接合。升高溫度可軟化材料硬度,同時降低接合所需壓力。然而如果金屬表面有氧化物存在時,則會抑制接合面之晶粒成長,所以金屬表面不能有氧化物存在。

目前3D IC最常應用之金屬熱壓接合為銅對銅(Cu-Cu)晶圓接合,銅對銅晶圓接合技術必須注意兩大重要參數:溫度均勻性與壓力均勻性。至於最大接合溫度之高低,則由元件的熱預算(Thermal Budget) 所決定。在溫度均勻性參數方面,如果能夠增加溫度均勻度,則可提高加熱速度,進而提昇產能。然而,如果晶圓表面溫度分佈不均,則會在局部區域產生扭曲,以 及在接合層產生內應力,進而嚴重影響接合品質。在壓力均勻性參數方面,有良好均勻的壓力分佈,可以補償晶圓的不平整性,以及晶圓厚度變化等缺失。

銅對銅的熱壓接合製程有兩種:第一種使用銅與原生氧化物(Native Oxide);第二種使用銅與有機鈍化層(如BTA),此鈍化層是在銅雙鑲嵌製程(Copper Dual Damascene Process)的Post-CMP清洗時沉積於金屬表面。為了接合成功,這些位於金屬表面之原生氧化物(Native Oxide)及有機鈍化層(Organic Passivation Layer)必需於接合前清除,它們的去除可在原來接合腔體(Bond Chamber)中進行,或者結合原位(In-Situ)與異地(Ex-Situ)製程中進行。原位(In-Situ)製程是將兩晶圓加熱到大於300℃維持幾分鐘,以蒸鍍法鍍上BTA層,它是在鈍態或反應性氣氛下進行(N2,蟻酸,或形成氣體(5%H2+95%N2或Ar))。將晶圓在蟻酸(Formic Acid)內或形成氣體環境下(Forming Gas Ambient),維持在300℃額外數分鐘(時間與Oxide厚度有關),如此可大大降低原生氧化物的形成。為了增加產能,有些製程是在接合腔中使用短時間之熱壓接合,僅施以接觸力來啟動原子擴散,後續於爐子內則不施以接觸力,只進行熱退火來完成原子擴散。

最新發展出一種常溫銅對銅熔融接合製程,它與Oxide-Oxide接合相似。此製程必須將銅表面拋光到粗糙度小於1nm,然後將銅表面做化學處理,使銅表面達到親水性。先將晶圓於常溫下做預接合(Pre-Bonding),然後在400℃下做熱退火(Thermal Annealing)來進行銅的擴散,此技術除了具備高產能的優勢外,使用常溫預接合製程可提高對準性精度,也是它的一項強項優勢。

3.3. 聚合物黏著接合(Polymer Adhesive Bonding)

聚合物之晶圓接合不需要特殊表面處理,例如:平坦化與過度清洗(Excessive Cleaning)步驟。聚合物接合對於晶圓表面之顆粒污染物較不敏感,一般常使用於晶圓接合的聚合物,則包括:熱塑性聚合物(Thermoplastic Polymers)及熱固性聚合物(Thermosetting Polymers)兩種。欲接合之兩片晶圓表面,首先旋轉塗佈液態聚合物,加熱以去除溶劑,以及形成聚合物交鏈作用(Cross-Linking)。然後將兩片晶圓於真空壓力下小心進行對準及接合,接著在真空環境下烘烤,以形成強而可靠的接合界面。聚合物晶圓接合種類,包括:負光阻、BCB(Benzocyclobutene)[6, 7~9]、Parylene及Polyimide [10]等,其中BCB具有傑出的晶圓接合能力、抗化學腐蝕性、以及具備良好接合強度。

針對BCB材料需要進行預烘烤(Pre-Cure)步驟,以去除溶劑及強化高分子聚合物,如此可防止後續壓合時產生歪斜,進而改善整體的對位精準度,預烘烤溫度為190℃,時間為1.5~3分鐘。BCB聚合物接合可在大氣環境或真空壓力下進行,然而在真空壓力下即能防止外圍空氣污染,又可在加熱昇溫時將殘留溶劑迅速抽離排出。BCB聚合物接合溫度為220~320℃,時間為30分鐘 [8]。

負光阻與Polyimide皆可使用氧電漿(Oxygen Plasma)進行蝕刻,所以非常適合於犧牲性接合層(Sacrificial Bonding),或3D整合平台(例如MEMS應用)之暫時性接合應用上。圖八為使用BCB聚合物,將具有銅-氧化物互連結構之晶圓與玻璃進行接合,然後經由研磨、拋光、濕式蝕刻等步驟,以去除矽基板之照片。使用聚合物做為接合層,可在200-300℃低溫下進行接合,此法之優點:(1)接合溫度低;(2)晶圓表面潔淨度要求不高;(3)與標準CMOS晶圓製程相容;(4)可接合任何晶圓材料。然而,在接合與烘烤製程上則容易產生對位不準問題,這是聚合物接合目前尚待克服之技術瓶頸。

圖六:使用電漿活化改變晶圓表面之化學構造,以形成高能量鍵結,可降低退火溫度及退火時間。

圖七:不同退火溫度(100、200、300、400℃)下,晶圓接合強度(表面能)與退火時間之變化圖。

圖八:使用聚合物進行接合之照片 [6]。

4. 結論

目前晶圓接合(Wafer Bonding)已公認為3D IC整合的關鍵步驟之一,此製程是將個別獨立之晶圓進行對準(Alignment)及接合(Bonding),以實現層對層導線連接之目的。本文已針對晶圓對位及接合技術之基本性質,以及接合的關鍵技術等,進行詳細探討。晶圓接合操作步驟,包括:晶圓表面準備及清洗、晶圓對位、晶圓接合和接合後之量測等。近年來由於3D IC技術的迅速發展,進而帶動晶圓接合技術朝向12"晶圓及各種先進TSV技術整合上發展。

參考文獻:

1. V. Dragoi, “From Magic to Technology: Materials Integration by Wafer Bonding,” SPIE Proceedings, vol.6123, 2006, PP 612314-1-15.

2. Banqiu Wu, Ajay Kumar, Sesh Ramaswami, “3D IC Stacking Technology”, ISBN 978-0-07-174195-8, 2011, pp 409~435.

3. L. Di Cioccio, “New Heterostructures & 3-Dimensional Device Obtained at CEA/Leti by the Bonding & Thinning Method,” ECS Trans., vol. 3, no. 6, 2006, pp 19.

4. V. Dragoi, P. Lindner, “Plasma Activated Wafer Bonding of Silicon: In Situ & Ex Situ Processes; “ ECS Tyrans., vol. 3, no. 6, 2006, pp 147.

5. P. P. Morrow, C. W. Park et. all, 3-D Wafer Stacking via Cu-Cu Bonding Integrated with 65nm strained-Si/Low-K CMOS Technology,” IEEE Electron Dev. Lett., no. 5, 2006, pp 335~337.

6. Through Silicon Technologies, “Through-silicon-vias” available on the website: http://www.trusi.com/frames.asp?5 (Access date: Dec. 4, 2007).

7. J.-Q. Liu, A. Jindal, et all, “Wafer-level assembly of heterogeneous technologies, “The International Conference on Compound Semiconductor Manufacturing Technology, 2003, available on http:// www.gaasmantech.org/Digests/2003/index.htm (Access date: Dec. 4, 2007).

8. C. Christensen, P. Kersten, S.Henke, and S. Bouwstra, „Wafer through-hole interconnects with high vertical wiring densities, “IEEE Trans. Components, Packaging and Manufacturing Technology, A, vol. 19, 1996, p.516.

9. J. Gobet et all, “IC compatible fabrication of through wafer conductive vias,” Proc. SPIE-The International Society for Optical Engineering, vol. 3323, 1997, pp. 17~25.

10. M. Despont, U. Drechsler, R. Yu, H. B. Pogge, and P. Vettiger, Journal of Microelectro-mechanical System, vol. 13, no.6, 2004, pp.895~901.

原文請參閱《半導體科技雜誌 SST-AP Taiwan》

|