延長摩爾定律的工作將越來越依賴高精密製程技術以製作出具有高品質薄膜表面的微小元件。在小於14奈米的技術節點中,電晶體的性能非常容易受到的製程變異的影響,會造成漏電流升高及電池耗電的現象。針對這些挑戰我們可以預期在未來的10年內,電晶體的柵極尺寸將低於50個原子寬度,特徵尺寸的變異將以原子等級的尺度測量,包括表面粗糙度的影響。原子層製程技術是最有機會達到這一精度等級的技術。原子層沉積(atomic layer deposition, ALD)在半導體產業中已經在生產線上存在了十多年。然而與其相對應的製程,也就是原子層蝕刻技術(atomic layer etching, ALE)卻難以成熟,原因在於它的生產能力還不足以達到所需的成本效益,此外商業化的設備系統也還沒有推出市場。本文我們將提出一種以商用電漿反應器開發的電漿增強ALE,可提供原子級的精準度並適合大量生產的元件製程技術。

原子層技術的優點

雖然已經應用在半導體產業中將近40年,連續式的沉積和蝕刻技術還是因為它們的製程原理而在本質上無法相當精確。通常情況下,所有的反應物會被同時引入反應室,在那裡它們同時而且連續地與裸露的晶片表面產生反應。其結果是膜的厚度通常與某些參數有極密切的相關性,例如反應物的通量(flux)可以造成局部 或是整片晶圓的變化。雖然連續式的製程可以加以優化以提高精確度,例如均勻性和膜的平滑性,然而往往難以同時優化所有的參數。

相反地原子層技術是依次藉由一套重複的自限制(self-limiting)循環步驟將反應物引入。在這種情況下膜的增厚或減薄是通過這些循環的次數來控 制。表面反應會在有限的反應物消耗之後停止,另外每一個週期結束之後薄膜表面會「復位」(reset)到普通狀態。如此從根本上可獲得一個光滑且均勻的膜表面。

在大量生產時若欲採用原子層製程,面臨的挑戰是它們的生產速率往往太慢,可能比連續式製程少幾個數量級。以ALD來說,晶圓廠在實驗室開發出這項技術將近半個世紀後才採用,也比其他產業(如平板顯示器)更晚將其帶入商業化應用。今日ALD已經是金屬和電介質沉積的主流技術。儘管ALD的速率仍低於某些化學氣相沉積(chemical vapor deposition, CVD)等連續製程,但是ALD的獨特優點仍然具有相當的吸引力,尤其是對於非常薄的薄膜,或者是替代技術還達不到要求的時候。持續改善ALD的生產速率讓ALD未來將會被應用在越來越多的新型薄膜製程中。

讓ALE加快

落後於相對應的沉積技術,ALE首次在實驗室中出現已經是90年代初期的事,並且一直算是一項重要的研究課題[1]。不幸的是,要達到足夠的生產速率讓大量製造變為可行的過程充滿許多挑戰。這裡以研究最多的ALE矽薄膜蝕刻來說明生產速率的問題。已揭露的週期時間通常在1分鐘至5分鐘左右,對應的蝕刻速率從〜0.1到〜0.01奈米/分鐘。如此長的加工時間主要是因為採用熱吸附法(adsorption)、以及用專屬設備(例如離子束系統)進行解附(desorption)過程,這些步驟從成本角度來看都是無法接受的。真正具吸引力的替代方案是使用常規的蝕刻反應器,然後藉由特殊的電漿技術增強ALE的蝕刻速率。

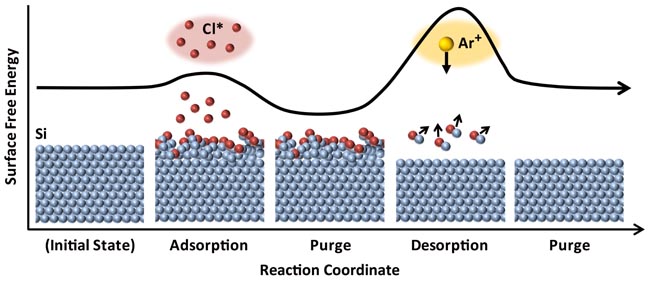

為了瞭解電漿增強技術是如何改善製程的週期時間,在此詳細分析一個ALE週期的各個步驟。圖1顯示以氯(Cl2)和氬(Ar)蝕刻矽的案例研究。首先,氯的反應物被吸附到矽表面,然後過量的反應物被清除。接著藉由定向離子轟擊將氬離子引入以解附矽氯化合物等副產物,之後再清除過量的氣體。這些步驟重複循環進行,直到到達預定的去除厚度。

圖1. 以氯和氬氣蝕刻矽膜的電漿增強ALE循環步驟。

吸附步驟過去都是以熱製程完成,吸附作用會自發地在室溫下發生,並且遵循 Langmuir的吸附動力學。據文獻所載,要讓表面進入完全飽和狀態所需的時間大約30秒。此步驟的速率是被氯分子的解離速率所限制,解離動作務必在氯氣與表面的矽斷鍵開始反應前發生。採用電漿增強的ALE方法,氯氣會被點燃成電漿,從而完全解離並產生自由基以迅速地和矽表面產生反應。值得一提的是,在電漿的操作區間內必須最大限度降低離子和光子的能量使其不高於蝕刻發生的門檻,如此是為了防止過早且不受控制的蝕刻誤動作。

至於解附(desorption)步驟,轟擊粒子的目的是提供足夠的能量來切斷因為吸附氯氣而變得脆弱的Si-Si鍵。然而以轟擊表面的方式來移除材料的 效率並不高,根據計算大約每10顆粒子才能除去一顆氯化矽副產物分子[2]。這個步驟可以藉由施加大量的轟擊離子予以加速,而且這些轟擊離子是在相同的電 漿反應器中產生。藉由改善這些吸附/解附過程以及加入快速氣體交換功能,循環次數可以顯著地提高。

電漿增強ALE之應用

此ALE技術是在整片磊晶圓上與連續式電漿用相近條件的狀態下進行比較。發現ALE製程的蝕刻速率明顯地比傳統技術的速率快上許多。為了確認ALE製程不是只有簡單的物理濺射和自發性的化學表面反應,這些速率經測量確認對提升整體蝕刻速率並無顯著地助益。同時也證實電漿增強ALE製程是 有其自限性,反應層只有幾個原子深的厚度。需要注意的是,與ALD相似,ALE製程的優點不是因為每個週期恰好就刪除一個原子層,而是由於每個週期都具有 自限的能力。

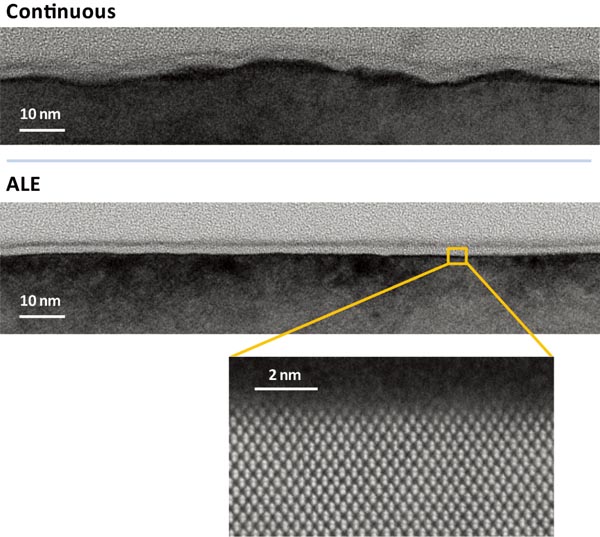

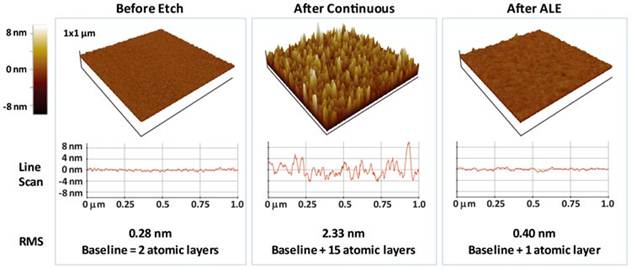

為了評估蝕刻之後的表面狀態,整片晶圓再以連續式或ALE製程除去約400個矽原子層(約50奈米),並用高解析透射電子顯微鏡(TEM)(圖2)進行評估。連續式製程會產生粗糙的表面,而ALE製程則留下光滑的表面。表面粗糙度的量化分析是利用原子力顯微鏡(AFM)以及均方根(RMS)數值法加以分析。在蝕刻之前,其表面粗糙度為2個原子層(圖3)。數據顯示連續式製程由於累積效應所致,粗糙度會增加15個原子層。與此相反,ALE製程的粗糙度只額 外增加一個原子層,從而保持膜的平滑度。這樣的結果可歸因於ALE的自限性質讓薄膜的表面狀態在每次循環之後都會「復位」。

圖2. 在相近的製程條件下以連續式和ALE技術去除約400個原子層後,整片磊晶片在高解析TEM下之圖像。

圖3. 以AFM觀察整片磊晶片在蝕刻前,連續式蝕刻後以及ALE蝕刻後之表面粗糙度。

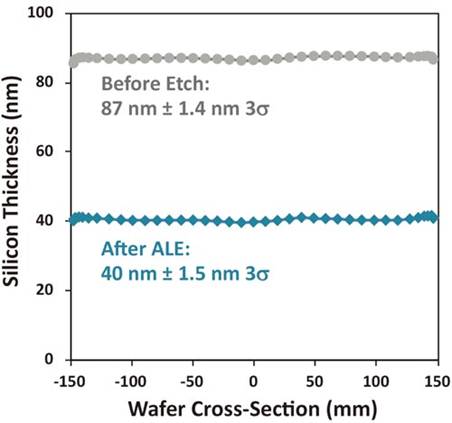

ALE製程在宏觀尺度下也一樣精準。測量整片300毫米晶圓以ALE製程去除的 矽數量(圖4)。即使ALE製程還沒有優化,它一樣表現出優異的均勻性,這表明此製程對出現在整片晶圓上的中性物質和離子的變化較不敏感。這也意味著此製 程具有較高的製程穩定性與可重複性,而這些特徵是決定此一技術能否應用在大量生產的重要條件之一。

圖4. 整片矽晶圓在ALE之前和之後的均勻性。

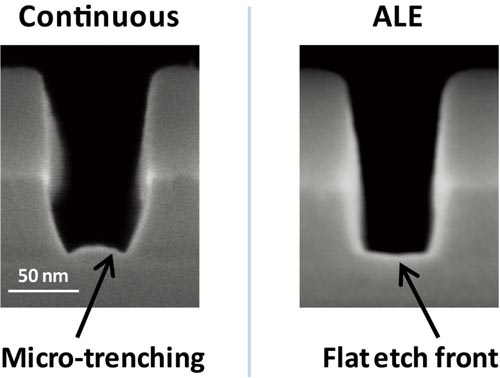

為了檢視此製程蝕刻圖形的能力,此處以多晶矽溝槽來檢視蝕刻輪廓。如圖5的掃描 式電子顯微鏡(SEM)圖像所示,連續式製程的蝕刻前端呈現微溝槽(micro-trenched)輪廓,眾所周知這是發生在氯/氬氣電漿化學反應中。這 種效應歸因於離子被側壁散射,導致溝槽側角落的蝕刻速率比中心更快[3]。與此相反,ALE的蝕刻結果呈現一個平坦的蝕刻前端。這是因為該製程的自限制特性:一旦被吸附的反應物耗盡時,氬氣的濺射率便大幅降低。總的結果是得到平坦的蝕刻前端,並且具有原子級的平滑表面,均勻地在整片晶圓上重複出現。

圖5. 以相近的製程條件進行多晶矽溝槽蝕刻後的SEM圖。

結論

本文提出的電漿增強ALE技術可提供原子級的蝕刻精準度,同時具有合理的製程時間讓其可應用在產線之中。此技術一方面解決傳統生產速率 低的問題,另一方面以市售的蝕刻反應器藉由增強吸附和解附步驟以達到自我限制的特性。有了這項新功能,可立即投入生產的ALE就立刻成形。這對延長摩爾定 律來說是一個重要而且令人興奮的里程碑。SST-AP/Taiwan

原文請參閱《半導體科技雜誌 SST-AP Taiwan》

|