本文闡述如何在碳化矽晶圓背面蝕刻出85μm直徑、100μm深孔的製程技術。

氮化鎵(GaN)的高崩潰電壓和高電子遷移率使其成為高功率元件應用上極具吸引力的材料。氮化鎵通常在碳化矽(SiC)晶圓上成長,因此,需在碳化矽晶圓的背面製作深蝕刻孔,以形成導電通路到碳化矽晶圓正面電路。

相較於砷化鎵(GaAs)而言,碳化矽和氮化鎵的材料性質使得它們在電漿蝕刻方面更具挑戰性。首先電漿的能量需要相當的考量,不僅要兼顧到碳化矽蝕刻速 率,同時要保持對遮罩層足夠高的選擇性蝕刻和低至不影響晶圓的溫度,使晶圓能保持粘合、避免沉積層膜剝離。這需要用到金屬遮罩、仔細注意晶片夾持方法和腔 體溫度控制。由於預蝕刻碳化矽表面清除浮渣的步驟,其目的是在減少通孔中的缺陷,因此以最大限度地提高設備的產量來說此步驟是不可或缺的。在這樣一個充滿 電漿游離氣氛環境中,要同時保持足夠光滑的碳化矽表面以接續後續的金屬沉積/電鍍製程,還要防止對氮化鎵選擇性蝕刻是非常具有挑戰性的。為了使產品能有相 對較低的波動性蝕刻,在組裝前需要同時且有效的為晶片和反應器做濕式清洗。

實驗

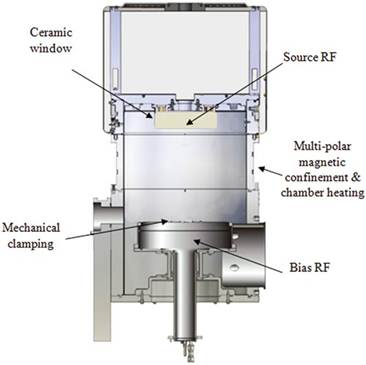

電漿蝕刻用的基板由穩懋半導體製備:直徑100mm的氮化鎵/碳化矽陶瓷基板被暫時性的面朝下黏於100mm的載具上。碳化矽研磨至約 100µm厚度之後,電鍍上一層具蝕刻圖案的鎳遮罩於碳化矽之上。通過蝕刻的晶片接下來的一道製程是濕式清洗,用以清潔光罩及光阻聚合物。然後對氮化鎵層 進行蝕刻,使用碳化矽層做為光罩,蝕刻終止點於晶圓正面的Au金層。所有的蝕刻都是在SPTS的APS製程腔體內進行。APS電漿蝕刻腔體圖如圖一所示。

圖一:APS電漿蝕刻腔體的示意圖。

反應器設計為具有環形外觀的射頻耦合的陶瓷電漿源(13.56MHz,2.2kW),和一個加熱腔體(設置50〜60℃)與多極磁約束。這種設計的電漿密度範圍為1012-1013cm-3,通常比傳統的感應耦合電漿離子矽蝕刻系統(ICP System)高10倍。

蝕刻過程中分別使用SF/O/He和Cl/BCL化學氣體來對碳化矽和氮化鎵進行蝕刻。除渣是為了減少/消除支柱缺陷的形成,因此發展作為碳化矽蝕刻製程 的其中一個步驟。機械夾制具用來確保在碳化矽及氮化鎵蝕刻步驟時溫度控制的可靠度。平板溫度設定為10℃。光學發射光譜(OES)用來確認氮化鎵蝕刻的結 束點。濕式清潔的製程也同時被觀測。蝕刻過後的晶片使用光學顯微鏡、掃描式電子顯微鏡、表面輪廓儀和溫度測量標記來進行分析。

結果

晶片溫度由RS公司以'4 level micro strips '進行了量測。這些溫度貼紙記錄溫度峰值變化。表一總結了多種類型的晶片在平板設定為10℃時,5分鐘蝕刻過後的溫度峰值。以暫時貼合製程載具而言的最大 容許溫度是130℃,而這些晶片的溫度都遠低於安全的範圍內。

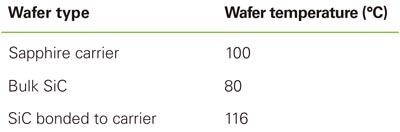

表一:不同種類的晶圓蝕刻之晶圓溫度

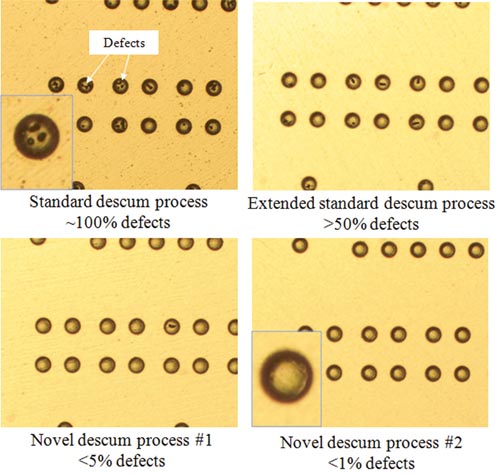

由於濕式清潔過程中,金屬種晶層和碳化矽研磨層都會或多或少的受到一點蝕刻效應而產生微細粒子,因此在蝕刻前處理需額外增加一道去殘留物的清潔製程。就如 圖二所示的碳化矽孔光學圖像顯示,在部分蝕刻過後進行局部的清除。標準的去殘膠製程是無效的,反而會導致50-100%的缺陷產生。一個專門去殘膠的製程 已經開發出來,使支柱缺陷降低至<1%。

圖二:光學圖像顯示去殘膠條件對支柱缺陷密度的影響。

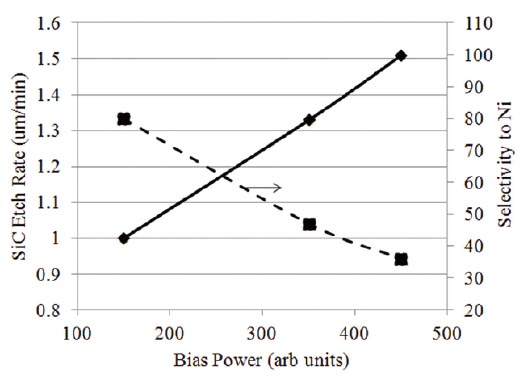

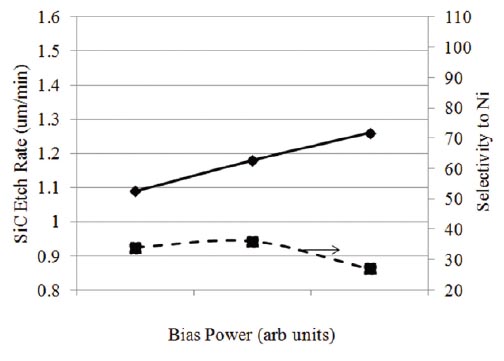

圖三顯示為碳化矽蝕刻速率和鎳遮罩的選擇性為主要蝕刻條件,相對於偏壓功率所做出來的函數圖形。晶圓除渣對蝕刻速率和選擇性的影響,已透過優化製程的條件而可忽略不計。

圖三:碳化矽蝕刻速率相對於鎳光罩選擇性和偏壓功率之關係。SF6/O2/He流量比10:1:7。

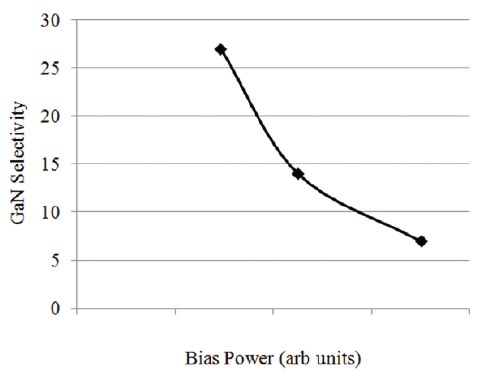

數據清楚地表示,通過蝕刻選擇性的最佳化設計,可以在最大蝕刻速率和節約足夠的鎳遮罩之間取得一個平衡。圖四顯示為氮化鎵底層蝕刻選擇性與偏壓功率範圍。可藉由降低偏壓功率,來提高蝕刻選擇性。

圖四:碳化矽:氮化鎵蝕刻選擇性比與偏壓功率。SF6/O2/He流量比10:1:7。

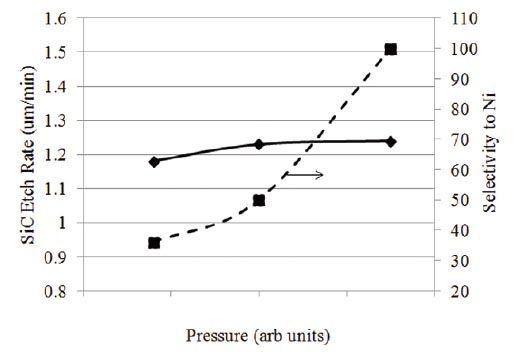

觀察蝕刻速率和選擇性的趨勢,有必要改善側壁粗糙度。圖五所示為化學稀釋液在碳化矽對蝕刻速率與光罩選擇性的影響。氦氣流量的增加也會影響主製程氣體。圖 中可看出相對應減少的趨勢。在這些條件下可得到較低的蝕刻速率,而蝕刻選擇性相對於偏壓功率的函數,也相對的可以在調整蝕刻的過程中得到一些緩衝的幫助。 化學液的稀釋對於改善側壁表面粗糙度以及提高晶圓蝕刻率的均勻性有顯著影響。下一個階段的研究可以朝更高的製程壓力對碳化矽蝕刻速率及蝕刻選擇性提昇,同 時保持側壁表面粗糙度來發展。圖六表示碳化矽蝕刻速率、蝕刻選擇性與製程壓力之間的趨勢。

圖五:碳化矽蝕刻速率相對於鎳光罩選擇性和偏壓功率之關係。SF6/O2/He流量比10:1:25。

圖六:碳化矽蝕刻速率、光罩選擇性與製程壓力之間的關係。SF6/O2/He流量比10:1:25,偏壓功率350W。

表二總結為碳化矽蝕刻最佳化調整的製程趨勢。

表二:碳化矽孔蝕刻製程趨勢

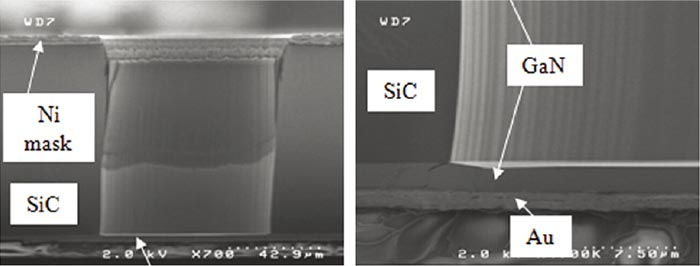

圖七所示的電子顯微鏡截面圖為100µm深的碳化矽晶圓經由兩個步驟的最佳化調整後,蝕刻終止於氮化矽層。此製程中的氮化矽層損耗經測定<0.35µm。

圖七:100µm深的碳化矽晶圓蝕刻停止於2µm的氮化矽阻擋層。氮化矽層的消耗測定 <0.35µm。

圖八表示以相同的APS電漿膜組,使用Cl/BCL化學氣體對碳化鎵的蝕刻。這個製程的順序是在鎳遮罩已經被去除後,接續濕式清潔在光阻聚合物之前,選擇性的蝕刻掉氮化鎵層以使金層露出。

圖八:氮化鎵蝕刻後的碳化矽底部。

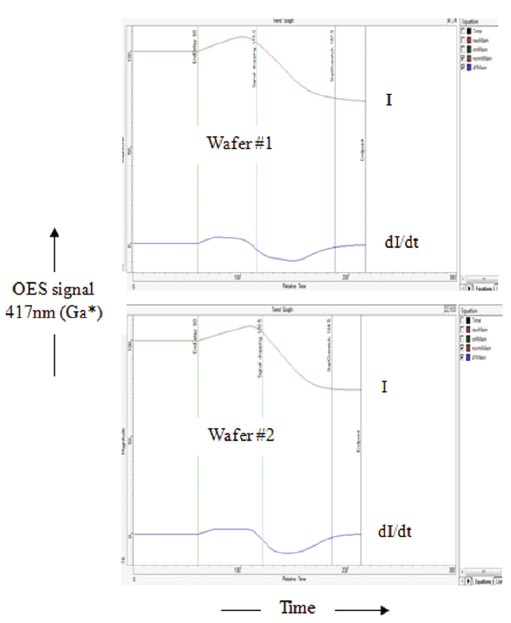

氮化鎵蝕刻終點軌跡表示於圖九。元素鎵的光譜是在417nm,連續2個晶圓蝕刻的強度驗證僅需3秒即可完全蝕刻。

圖九:OES檢測連續2晶圓,氮化鎵蝕刻終點停止於金層。

使用20%的硝酸溶液(HNO3)在室溫下15分鐘,即可將聚合物的清潔,如圖十所示。溝槽中的底部的孔可見得典型電漿蝕刻的痕跡。當蝕刻到氮化矽層時這些痕跡就會消失。

圖十:在20%的硝酸15分鐘,蝕刻前後的殘留聚合物皆去除。

後續的製程是在基板的孔上沉積一層金屬種晶層和電鍍金,致使電阻率低於6E-3Ω。

結論

碳化矽背面蝕刻製程可應用於高功率元件的製備。蝕刻速率>1.3μm/min、蝕刻均勻性<±5%可在30-40:1的鎳 光罩選擇性中達成。導入獨特的去殘膠製程可使支柱缺陷<1%,而孔中殘留聚合物可使用硝酸水溶液清潔。同一電漿模組可以用於蝕刻氮化鎵,且具有自動 蝕刻終點檢測,已控制蝕刻點停在金層。電鍍後的電阻率<6E-3Ω。

原文請參閱《半導體科技雜誌 SST-AP Taiwan》

|