從近日閉幕的會議以及即將到來的會議中透露出來的消息顯示傳統與新型的電子元件面對的未來將是一片光明。這些新興的電子元件主要包括矽元件、軟性基板、石墨烯與奈米線。

當談到下一世代電子元件時,FinFET早已經是眾所矚目的焦點。不過主要來自Intel在內的各家廠商在相關技術上的發展仍然持續地進行著。在十二月即將舉行的國際電子元件會議(International Electron Devices Meeting,IEDM)中,Intel將展示他們如何開發出一個完整的系統晶片(system-on-chip,SoC)平台。而這不過是在IEDM與其它會議中(如六月舉行的VLSI Symposium)聽到的許多令人興奮的消息之一。

|

|

過去在軟性基板上已經有許多高等電路的實作成果,這些成果在未來有可能演變成捲筒式的IC製程。雖然時至今日,由於塑膠基板不能在高溫與惡劣的製程環境中製造出高效能的CMOS元件,以致於軟性電子電路的功能十分有限。然而在IEDM會議上將頭一次公布一種避免此問題的方法。由來自IBM的研究人員將展示在軟性塑膠基板上建構出高性能且是目前最尖端的CMOS線路,包括SRAM記憶體與環式振盪器。

IBM採用的方法是絕緣物上超薄矽元件技術(extremely thin silicon on insulator,ETSOI),它的主體厚度只有60Å。IBM以矽材料製造這些元件然後再用一種簡單、低成本、常溫的製造方法(稱為受控剝裂,controlled spalling)處理之後將它們轉移到軟性塑膠基板上。

此元件的閘極長度小於30nm,閘極間距是100nm。環式震盪器在0.9V時的各階延遲僅僅16ps,據信這應該是軟性電路上已知的最佳表現。

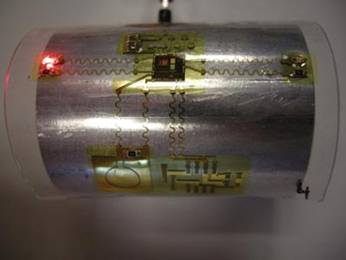

IMEC是位於比利時的一個半導體技術聯盟,最近他們也宣稱可以把超薄可彎曲的晶片,以及可彎曲、可延展的內連線,一起整合在同一封裝當中。這項技術可以動態地適應弧狀與彎曲的表面(圖1)。如此形成的電路在未來可以嵌入醫療器材或生活應用中,例如監控身體狀況或是智慧衣著,提供給將舒適感以及低調列為首要需求的使用者使用。

圖1 IMEC將超薄且具彈性的晶片與可彎曲且可伸展的內連線整合在同一封裝中,可應付弧狀或彎曲的表面。

FinFETs的新貌

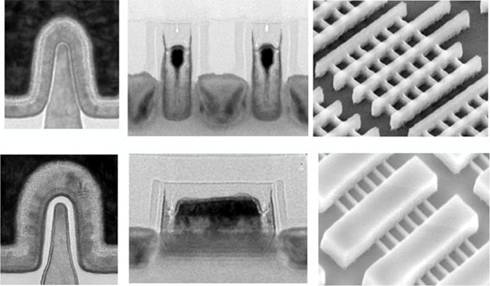

多閘式電晶體,例如FinFET(或Intel說的”三閘式”電晶體)可以提供較佳的開關控制,同時可以比其他元件在更低的電壓下輸出更高的驅動電流。在IEDM中,Intel將展示他們如何開發出包括高速、低待機功耗與高耐壓等數種FinFET”家族”(圖2),另外還將展示最新的內連線結構以及可以廣泛應用在SoC上的RF/混頻特性。

圖2 Intel將推出兩種版本的三閘式電晶體,一種是給邏輯電路(上)使用,而另一種是給高壓電路使用(下)。所有的元件都整合於一個SoC中。資料來源: Intel

高速邏輯電晶體的次臨限漏電範圍在100nA/µm與1nA/µm之間,而低功耗版本具有漏電小於50pA/µm而且它的驅動電流比32nm平坦型元件(傳統技術)還高50%。此製程也開發高耐壓電晶體(1.8V or 3.3V)以提供類比電路、I/O、傳統設計與其他方面的應用。以SoC技術來說,它們具備目前已知的最高I/O元件的驅動電流能力(NMOS/PMOS=0.92/0.8mA/µm at 1.8V)。此三閘技術平台也具有8到11層的low-k與ultra low-k的碳摻雜氧化物(carbon-doped oxide,CDO)內連線且元件間距緊密可做不同應用;還具有許多類比/混頻訊號特徵;以及三種不同的SRAM位元元件,效能橫跨高密度/低漏電(0.092µm2),低電壓(0.108µm2)與高性能(0.130µm2)等三種特性。

ETSOI

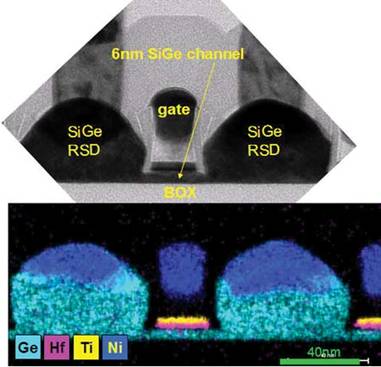

另一項在電晶體領域令人振奮的消息是超薄SOI(ETSOI)技術的發展。它快速地崛起成為CMOS微縮到22nm以下的可行元件結構之一。它具有優異的短通道控制能力以及穩定的無摻雜通道特性。IBM的團隊在IEDM中將報告世界首見的高性能混合通道ETSOI CMOS元件(圖3)。在22nm尺寸下整合具有薄且均勻的應變SiGe通道的PFET,以及具有Si通道的NFET。一種新式的STI後製(STI-last)製程讓此混成架構成真。研究者以環式振盪器比較此元件特性,而此混成平坦式元件可超越任何文獻上已知的最快速度,在0.7V下訊號延遲時間僅11.2ps/stage,甚至比FinFET還好。

圖3 具有SiGe通道的PFET的電子顯微鏡圖像(上)與EDX(Energy-dispersive X-ray)圖像(下)。該元件具有6nm的通道厚度、22nm的閘極長度、100nm的接觸閘極寬度、high-k/金屬閘結構以及ISBD SiGe上提式源極與汲極。資料來源: IBM

未來的記憶體

當傳統以電荷儲存為基礎的記憶體正面臨微縮限制的危機時,數種所謂”新興記憶體”已經從實驗室的樣品變成整合性的產品。在這些新興的記憶體技術中,MRAM (Magnetoresistive random access memory,磁阻隨機存取記憶體)與其它新型記憶體相比已經有了令人印象深刻的進展,並且展現其能做為DRAM或SRAM後繼者的實力。MRAM資料是以磁阻的方式儲存。平行或反平行磁阻分別代表”0”或”1”。早期的MRAM要變換這些磁阻時是採用電流衍生的磁場加以改變,可是這種作法限制了微縮的可能性。直到ST(spin-torque,旋矩)MRAM的發明藉由注入旋極化(spin-polarized)穿隧電流解決了微縮的問題。在IEDM上,一篇邀訪性的論文將由Everspin Technologies的研究者發表介紹他們如何製造出目前容量最大的ST-MRAM,一個具有良好電性的64Mb的元件。這項工作成果顯示MRAM正快速邁向商業化階段。

今年稍早,在夏威夷Honolulu舉行的VLSI Technology Symposium,IMEC展示了非揮發性電阻RAM(Resistive RAM,RRAM)在效能與可靠度方面的突破性進展。

RRAM是未來非揮發記憶體的一項可行的元件技術,原因在於它具有高速、低功率、更好的微縮可行性,以及與CMOS技術相容等優點。它的操作方法是以電壓在金屬/絕緣物/金屬(Metal/Insulator/Metal,MIM)之間產生導通熱絲(filament)以控制電阻變化。以HfO2為基礎的RRAM系統已經證明其具有極佳的微縮能力(面積<10x10nm)以及高可靠度等優點,這些都受惠於在切換時氧原子在MIM結構中的運動模式可以有效地由電壓控制。

在較為傳統的記憶體方面,元件技術上的發展也一樣持續地進行著,特別是3D記憶體。來自旺宏的研究者將在IEDM上發表第一次以40nm以下尺寸製成的3D NAND快閃式記憶體。他們以垂直閘極但是水平通道的方式構成新的佈局架構,大幅減少字線(wordline)方向的特徵尺寸並且改善了元件可被製造的可行性。這新的架構也採用了新式”階梯式”位元線接觸窗製作方法以減少製程步驟與成本。最後的結果是一個具有八層的元件結構,同時字線的特徵尺寸是37.5nm,位元線是75nm,每串記憶體的數量是64,而核心陣列的效能是63%。研究者說這項技術不只具有比傳統20nm以下的2D NAND更低的成本,而且若在25nm的尺寸下製作,它將可以提供1Tb的記憶體容量。在那樣的尺寸下,旺宏的元件只會有32層,而垂直通道的3D可推疊NAND則幾乎需要100層才能達到相同的記憶體密度。

石墨烯,MoS以及奈米線

談到新興記憶體就不能不提到石墨烯以及其他可能的替代品。石墨烯被視為未來可能取代矽的材料之一,原因是它具有極佳的電流密度、遷移率以及飽和速度。然而以石墨烯製作的電晶體無法關閉,因為石墨烯幾乎沒有能隙。研究者開始分析一種新的2D材料—硫化鉬(molybdenum sulfide,MoS)—它具有與石墨烯類似不過有一些不一樣的特性,比如說寬能帶間隙以及可以直接製作電晶體與電路。在IEDM中,MIT帶領的團隊將展示以CVD製程製作出均勻、彈性、而且是單分子結構的MoS。它用兩層硫原子將鉬原子夾在中間的三明治結構。利用此材料的1.8eV的能隙來建構MoS電晶體以及簡單的數位與邏輯電路(一個NAND邏輯閘以及一位元的ADC轉換器)。此電晶體具有目前最快的遷移率(>190 cm2/Vs)、超高開關比108、目前最高的電流密度(~20µA/µm)與飽和電流,以及第一個用MoS製作的GHz 等級RF元件。

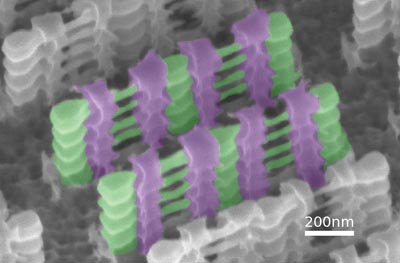

IEDM 還將展示另一項重要的進展: 在一些以矽、碳與石墨烯製作的奈米線電晶體中觀察到雙極性(ambipolar)導通的現象,也就是能在N型與P型之間切換的能力。在Lausanne的瑞士聯邦技術研究院(Swiss Federal Institute of Technology,EPFL)的研究人員在SOI基板上以垂直架構製成了閘極環繞式(gate-all-around)的雙極性矽奈米線FETs(圖4)。在奈米線的底端有”極性閘(polarity gate)”以控制元件的極性是N或P型,同時在中間有控制閘決定元件是開或關。此元件具有極佳的開關比例106,以及次臨限斜率70mV/dec。研究者也以邏輯閘的方式展示該技術可用於未來邏輯電路的可行性。

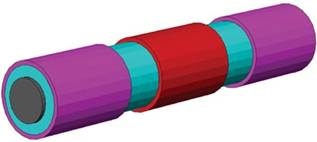

圖4a 電腦模擬顯示最佳的雙極性矽奈米線的元件結構,具有三個45nm長的閘極區域。

圖4b 以SEM斜角觀測堆疊的奈米線結構,此結構是在沉積與蝕刻極化閘之後進行觀測。

全文請參閱《半導體科技雜誌 SST-AP Taiwan》

更多歷期精采文章,請參閱智權報總覽 >>

|