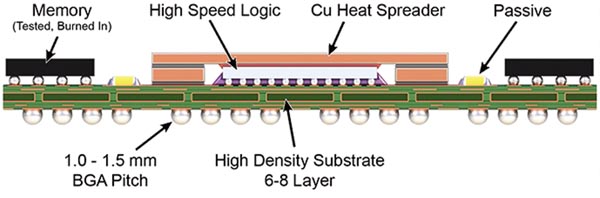

當涉及與外部裝置有許多輸入/輸出連結的複雜積體電路時,晶圓級封裝能擁有最低成本及最多功能。不同電路功能的整合 — 例如微型和圖像處理、現場可編程輯閘陣列(FPGA)邏輯‘動態與靜態存取記憶體、射頻(RF)和類比,以及感測和致動功能 — 或許也需要在封裝層級上下功夫,以能夠提供完整的系統(圖一)。

圖一:異質系統級封裝(SIP)是已驗證的覆晶(FC)封裝技術的延伸。

特別是在高成長的移動式通訊電子系統上的應用需要低功率和小體積的單位元件,因此不允許電路整合在印刷電路板上(PCB)。相反的,異質整合必須應用在系統級封裝(SIP)或系統單晶片(SOC)上。市場研究機構Yole Développement的Eric Mounier博士最近於Grenoble(格瑞諾布爾)舉行的歐洲3D TSV 2014高峰會發表了Yole的預測,顯示全球半導體IC晶圓被封裝在晶圓規模等級的比例在今年將達到19%,於2015年將提高到20%。

一個看IC產業歷史的角度是分析SIP和SOC方法之間的變動。新的功能傾向先被整合到硬體上成為新增的專有晶片,然後連結到系統的其他部分成為PCB或SIP的一部分。因為不同的功能經常需要不同的晶圓廠製程,一般而言在晶片層級將功能分拆到不同的晶片是比較便宜的,但相對的封裝成本就會比較高。產量相對低的元件也許最具經濟效益來做成SIP,而高產量的元件則較能證明其額外設計與測試費用的正當性,來提供相同的功能於單一的SOC中。

另一個採用SIP的主要原因是要改善晶圓廠先進製程的大面積晶片之良率。因為晶圓廠新製程的缺陷率/面積會相對較高,非常大晶片的設計往往一開始會有相對低的良率,但在晶圓廠知道如何降低隨機和系統性的良率限制因子後便會改善。最近這種趨勢的傑出例子是Xilinx(賽靈思)Vertex-7 FPGA,它的晶片被拆成四個子晶片,然後利用矽中介層讓SIP重新整合。我們可以預期下世代的產品在良率改善後將會建構在單一的SOC內,在那時可以預期賽靈思會延伸其產品線,使用多晶片SIP來增加額外的功能。

扇出型晶圓級封裝

Nanium S.A.的技術處長Steffen Kroehnert最近在2014新加坡半導體展(SEMICON/Singapore 2014)提出標題為「利用晶圓層級扇出的精細線距矽中介層」的演講。扇入型(fan-in)晶圓級封裝利用到晶片區域內封裝佈局的連結,當晶片上接線基板的尺寸和數目不符合標準封裝比例時,金屬連結的重佈層(RDL)將被用來扇入晶片區域內的球柵陣列或針型陣列(BGA/PGA)。然而,當在晶片區域內無法做出需要的連結數量時,將會使用封裝填充材料來提供原始晶片旁的實體區域,如此封裝連結便可安排成扇出型(fan-out)WLP,即從上方俯視時可以看到由晶片中心向外散的「扇出」狀。

根據Kroehnert的說法,晶片、封裝與印刷電路板的同步設計及同步研發越來越重要,取代以往的連續式工作。對於一個新SiP其再設計的成本與沒跟上上市時機的懲罰太高,以致於無法接受反覆的研發活動,因此產品必須在一開始就進行適當的同步研發。

FO-WLP憑藉了太陽能光電廠的訣竅

由賽普拉斯半導體擁有的電子互聯解決方案在半導體產業的提供商Deca Technologies最近宣布達成第一億件出貨。該公司歸功此里程碑的達成是因可攜式電子裝置製造商在使用Deca獨特的整合式Autoline生產平台製造的晶圓級晶片尺寸封裝(WLCSP)方面的強大需求,該平台設計的目的在以更低的成本實現更快速的上市時間。

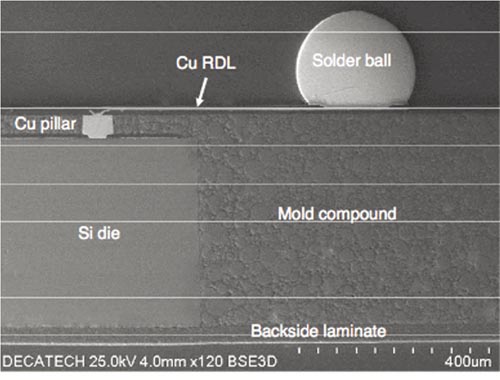

憑藉矽太陽能光電領導廠商SunPower Corp.的量產技術,Deca解決了半導體元件製造商使用傳統WLCSP製造方法所面臨的生產週期與資金成本的挑戰,因此能快速的達成此里程碑。Deca宣稱其他FO-WLP技術遭遇到因為矽模封材料介面的不連續性所造成的固有生產與可靠度問題,而他們本身則透過公司使用的銅柱和包覆成型技術(圖二)來克服。

圖二:使用銅柱和包覆成型技術的FO-WLP其邊緣截面圖(資料來源:Deca Technologies)

用於手機和可穿戴電子設備市場的無線連接、音頻和電源管理組件的製造商一直推動著對WLCSP的需求,這些市場的需求波動會產生管理庫存的挑戰。「恭喜Deca 團隊達成這個意義重大的里程碑,」ON半導體的全球供應鏈組織的資深副總裁Brent Wilson說道。「Deca的創新技術和對客戶服務的專注使該公司成為我們供應鏈中的一個重要部分。」

「達成1億件出貨對Deca而言是一個重要的里程碑,這證明了我們獨特的WLCSP製造技術」Deca Technologies的執行長Chris Seams如是說。「根據我們客戶所做的需求預測,我們預計今年出貨量可突破5億件。」

FO-WLP的未來

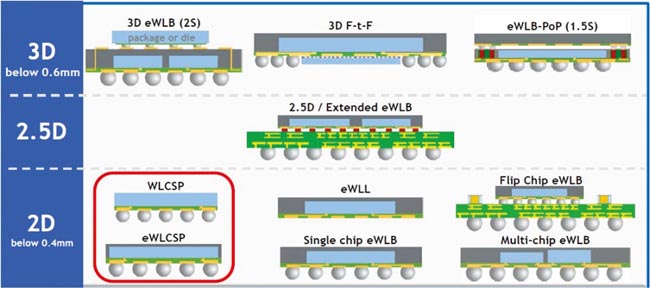

星科金朋半導體(STATSChipPAC, SCP)近期公布FlexLine FO-WLP。FlexLine製程會切割並重組進入產線的不同尺寸晶圓成為標準尺寸,如此讓晶圓級封裝設備可以不受進來的晶圓尺寸限制。此SCP FlexLine製造流程是根據SCP商用eWLB FO-WLP製程發展出來的(圖三)。自2009年起,單一和多晶粒扇出封裝解決方案已進入量產,到現在已出貨超過五億件。

圖三:各種扇出型WLP封裝的橫切面圖示。(資料來源:STATSChipPAC)

今年初時,電子時報(Digitimes)提供了一些中文每日經濟新聞(EDN)的簡短英文翻譯,提到台灣積體電路製造股份有限公司(TSMC)計畫在2015年提高IC封裝營收達美金十億元,並在2016年達美金二十億元。據報導台積電共同執行長魏哲家承認矽基底系統級封裝(台積電另稱chip-on-wafer-on-substrate或CoWoS)的生產成本相對較高,因此世界領先的積體電路代工廠傾向投資FO-WLP技術,期望能夠以較低的價格提供先進的封裝服務。

晶圓級封裝持續緩慢的獲取積體電路的市占,而新穎的扇出重佈技術則驅使著目前有嚴峻成本和可靠度限制的封裝材料之改善需求。憑著WLP技術的矽中介層和銅連接等要素,晶片和封裝之間的界線不會變得模糊。處理這些所有的複雜性是未來移動通訊系統設計時必然會遇到的事情。

原文請參閱《半導體科技雜誌 SST-AP Taiwan》

|

| Facebook |

|

按讚馬上加入北美智權報粉絲團 |

|

|

|

|

|

|

|

|

|